# DT9862 Series User's Manual

|   | _ |  |  |  |  |  |

|---|---|--|--|--|--|--|

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

| _ |   |  |  |  |  |  |

| _ |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

|   |   |  |  |  |  |  |

# Thirteenth Edition February, 2016

Data Translation, Inc. 100 Locke Drive Marlboro, MA 01752-1192 (508) 481-3700 www.datatranslation.com Fax: (508) 481-8620 E-mail: info@datx.com

#### Copyright © 2016 by Data Translation, Inc.

All rights reserved.

Information furnished by Data Translation, Inc. is believed to be accurate and reliable; however, no responsibility is assumed by Data Translation, Inc. for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Data Translation, Inc.

Use, duplication, or disclosure by the United States Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer software clause at 48 C.F.R, 252.227-7013, or in subparagraph (c)(2) of the Commercial Computer Software - Registered Rights clause at 48 C.F.R., 52-227-19 as applicable. Data Translation, Inc., 100 Locke Drive, Marlboro, MA 01752.

Data Translation® is a registered trademark of Data Translation, Inc. DT-Open Layers $^{\text{TM}}$ , DT-Open Layers for .NET Class Library $^{\text{TM}}$ , DataAcq SDK $^{\text{TM}}$ , LV-Link $^{\text{TM}}$ , and QuickDAQ $^{\text{TM}}$ are trademarks of Data Translation, Inc.

All other brand and product names are trademarks or registered trademarks of their respective companies.

#### **Radio and Television Interference**

This equipment has been tested and found to comply with CISPR EN55022 Class A and EN61000-6-1 requirements and also with the limits for a Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference, in which case the user will be required to correct the interference at his own expense.

Changes or modifications to this equipment not expressly approved by Data Translation could void your authority to operate the equipment under Part 15 of the FCC Rules.

**Note:** This product was verified to meet FCC requirements under test conditions that included use of shielded cables and connectors between system components. It is important that you use shielded cables and connectors to reduce the possibility of causing interference to radio, television, and other electronic devices.

#### **Canadian Department of Communications Statement**

This digital apparatus does not exceed the Class A limits for radio noise emissions from digital apparatus set out in the Radio Interference Regulations of the Canadian Department of Communications.

Le présent appareil numérique n'émet pas de bruits radioélectriques dépassant les limites applicables aux appareils numériques de la class A prescrites dans le Règlement sur le brouillage radioélectrique édicté par le Ministère des Communications du Canada.

# Table of Contents

| About this Manual                               | 11 |

|-------------------------------------------------|----|

| Intended Audience                               | 11 |

| How this Manual is Organized                    | 11 |

| Conventions Used in this Manual                 | 12 |

| Related Information                             | 12 |

| Where To Get Help                               | 13 |

| Chapter 1: Overview                             | 15 |

| DT9862 Series Hardware Features                 | 16 |

| Supported Software                              | 18 |

| Accessories                                     | 21 |

| Getting Started Procedure                       | 22 |

| Part 1: Getting Started                         | 23 |

| Chapter 2: Setting Up and Installing the Module | 25 |

| Unpacking                                       | 27 |

| System Requirements                             | 28 |

| Applying Power to the Module                    | 29 |

| Attaching Modules to the Computer               | 30 |

| Connecting Directly to the USB Ports            | 30 |

| Connecting to an Expansion Hub                  | 31 |

| Configuring the DT9862 Series Device Driver     | 33 |

| Chapter 3: Wiring Signals                       | 35 |

| Preparing to Wire Signals                       | 37 |

| Wiring Recommendations                          | 37 |

| High-Performance Considerations                 | 37 |

| Layout of the DT9862 Series Module              | 38 |

| Wiring Analog Input Signals                     | 40 |

| Wiring Analog Output Signals                    | 41 |

| Wiring Signals to the I/O Connector.            | 42 |

| Wiring Digital I/O Signals.                     | 46 |

| Wiring Counter/Timer Signals                    | 47 |

| Event Counting                                  | 47 |

| Up/Down Counting                                | 48 |

| Frequency Measurement                           | 49 |

| Period/Pulse Width Measurement                  | 50 |

| Edge-to-Edge Measurement                        | 50 |

| Continuous Edge-to-Edge Measurement             | 51 |

| Pulse Output                                                                               | 52   |

|--------------------------------------------------------------------------------------------|------|

| Wiring Quadrature Decoder Signals                                                          | 53   |

| Chapter 4: Verifying the Operation of a Module                                             | 55   |

| Running the Quick DataAcq Application                                                      | 57   |

| Testing Single-Value Analog Input                                                          | 58   |

| Testing Single-Value Analog Output                                                         | 59   |

| Testing Continuous Analog Input                                                            | 60   |

| Testing Single-Value Digital Input                                                         | 61   |

| Testing Single-Value Digital Output                                                        | 62   |

| Testing Frequency Measurement                                                              | 63   |

| Testing Pulse Output                                                                       | 64   |

| Part 2: Using Your Module                                                                  | . 65 |

| Chapter 5: Principles of Operation                                                         | 67   |

| Analog Input Features                                                                      | 69   |

| Input Resolution                                                                           | 69   |

| Analog Input Channels                                                                      | 69   |

| Specifying a Single Analog Input Channel                                                   | 69   |

| Specifying One or More Analog Input Channels                                               | 70   |

| Specifying the Digital Input Port in the Analog Input Channel List                         | 70   |

| Specifying Counter/Timers in the Analog Input Channel List                                 | 70   |

| Specifying Quadrature Decoders in the Analog Input Channel List                            | 71   |

| Input Ranges                                                                               | 72   |

| Input Sample Clock Sources                                                                 | 72   |

| Bandwidth of the DT9862                                                                    | 73   |

| Bandwidth of the DT9862S                                                                   | 73   |

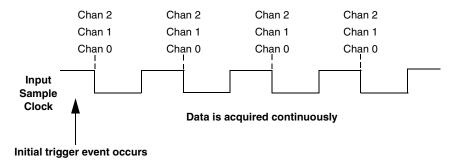

| Analog Input Conversion Modes                                                              | 74   |

| Single-Value Mode                                                                          | 74   |

| Continuous Scan Mode                                                                       | 74   |

| Maximum Acquisition Time for Analog Input Channels                                         | 75   |

| Maximum Acquisition Time for Digital Input, Counter Timer, and Quadrature Decoder Channels | 76   |

| Input Triggers                                                                             | 76   |

| Data Format and Transfer                                                                   | 77   |

| Error Conditions                                                                           | 77   |

| Analog Output Features                                                                     | 79   |

| Output Resolution                                                                          |      |

| Analog Output Channels                                                                     | 79   |

| Specifying a Single Analog Output Channel                                                  | 79   |

| Specifying Multiple Analog Output Channels and/or the Digital Output Port | 80  |

|---------------------------------------------------------------------------|-----|

| Output Ranges and Gains                                                   |     |

| Output Triggers                                                           |     |

| Output Clocks                                                             |     |

| Output Conversion Modes                                                   |     |

| Streaming Analog Output                                                   |     |

| Waveform Generation                                                       |     |

| Data Format and Transfer                                                  |     |

| Error Conditions                                                          |     |

| Digital I/O Features                                                      | 86  |

| Digital I/O Lines                                                         | 86  |

| Operation Modes                                                           |     |

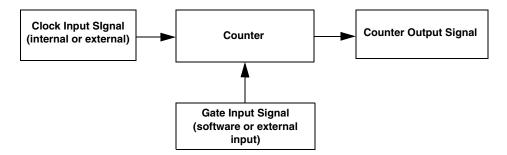

| Counter/Timer Features                                                    | 88  |

| C/T Channels                                                              | 88  |

| C/T Clock Sources                                                         | 89  |

| Gate Types                                                                | 89  |

| Pulse Output Types and Duty Cycles                                        | 90  |

| Counter/Timer Operation Modes                                             | 90  |

| Event Counting                                                            | 91  |

| Up/Down Counting                                                          | 91  |

| Frequency Measurement                                                     | 91  |

| Edge-to-Edge Measurement                                                  | 92  |

| Continuous Edge-to-Edge Measurement                                       | 93  |

| Rate Generation                                                           | 94  |

| One-Shot                                                                  | 94  |

| Repetitive One-Shot                                                       | 95  |

| Quadrature Decoder Features                                               | 96  |

| Chapter 6: Supported Device Driver Capabilities                           | 99  |

| Data Flow and Operation Options                                           | 101 |

| Buffering                                                                 | 102 |

| Triggered Scan Mode                                                       |     |

| Data Encoding                                                             | 102 |

| Channels                                                                  | 103 |

| Gain                                                                      | 103 |

| Ranges                                                                    | 104 |

| Resolution                                                                | 104 |

| Current and Resistance Support                                            | 104 |

| Thermocouple, RTD, and Thermistor Support                                 | 105 |

| IEPE Support                                                              | 106 |

| Bridge and Strain Gage Support                                            | 106 |

| Start Triggers                                      | 107  |

|-----------------------------------------------------|------|

| Reference Triggers                                  |      |

| Clocks                                              | 109  |

| Counter/Timers                                      | 110  |

| Tachometers                                         | 111  |

| Chapter 7: Troubleshooting                          | 113  |

| General Checklist                                   | 114  |

| Technical Support                                   | 116  |

| If Your Module Needs Factory Service                | 117  |

| Chapter 8: Calibration                              | 119  |

| Using the Calibration Utility                       | 120  |

| Calibrating the Analog Input Subsystem              | 121  |

| Connecting a Precision Voltage Source               | 121  |

| Using the Auto-Calibration Procedure                | 121  |

| Using the Manual Calibration Procedure              | 122  |

| Calibrating the Analog Output Subsystem             | 123  |

| Appendix A: Specifications                          | 125  |

| Analog Input Specifications                         | 126  |

| Analog Output Specifications                        | 128  |

| Digital I/O Specifications                          | 129  |

| Counter/Timer and Quadrature Decoder Specifications | 130  |

| External Trigger Specifications                     | 131  |

| Internal Clock Specifications                       | 132  |

| External Clock Specifications                       | 133  |

| Power, Physical, and Environmental Specifications   | 134  |

| Connector Specifications                            | 135  |

| Regulatory Specifications                           | 136  |

| External Power Supply Specifications                | 137  |

| Appendix B: Pin Assignments                         | 139  |

| Connectors on the DT9862 Series Modules             | 140  |

| I/O Connector (J11)                                 | 140  |

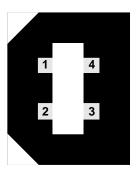

| External USB Connector (J6)                         | 142  |

| Internal USB Header                                 | 143  |

| External +5 V Connector (J5)                        | 144  |

| Internal +5 V Header (TB1)                          | 144  |

| STP78 Screw Terminal Panel                          | 146  |

| Annendix C: Ground Power and Isolation              | 1/10 |

| Appendix D: Register-Level Programming                    | 151 |

|-----------------------------------------------------------|-----|

| Reading the Setting for the Current Termination Resistor  | 152 |

| Changing the Setting for the Current Termination Resistor | 153 |

| Appendix E: Sample Frequencies and Data Rates to the Host | 155 |

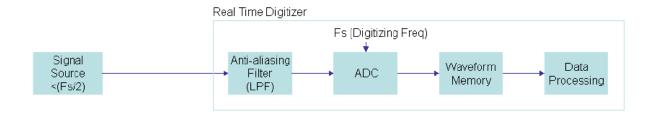

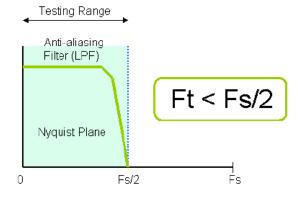

| Appendix F: Digitizing and Sampling                       | 159 |

| Introduction                                              | 160 |

| Preface to the Series                                     | 161 |

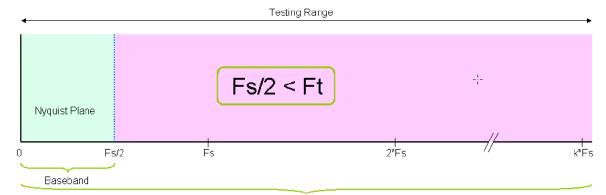

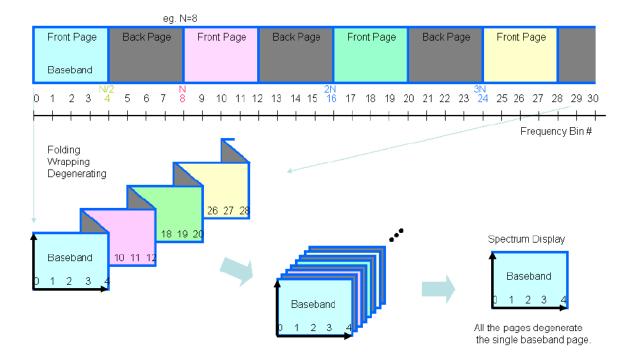

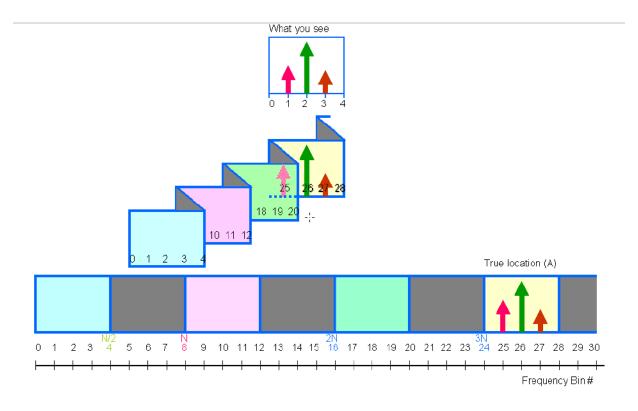

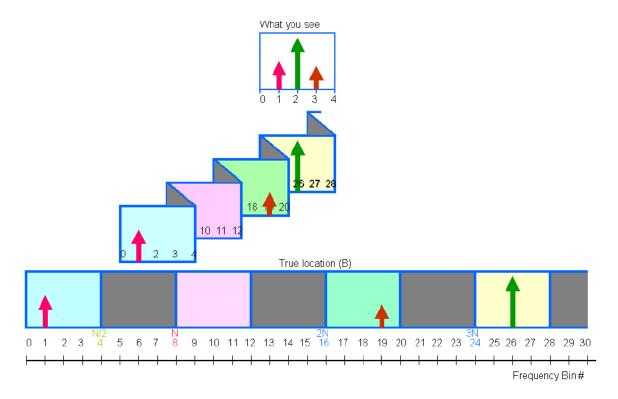

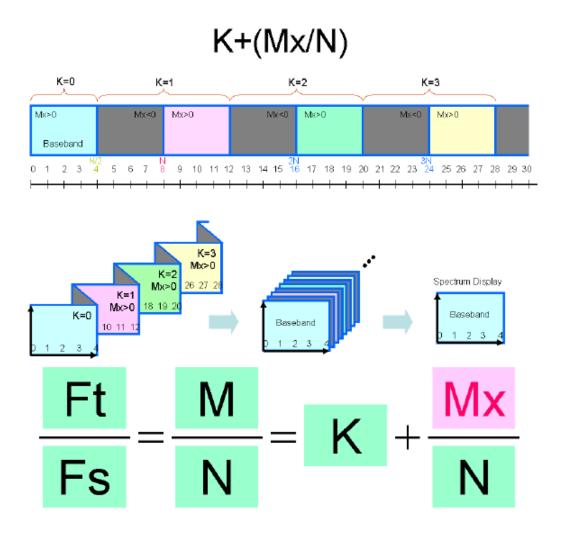

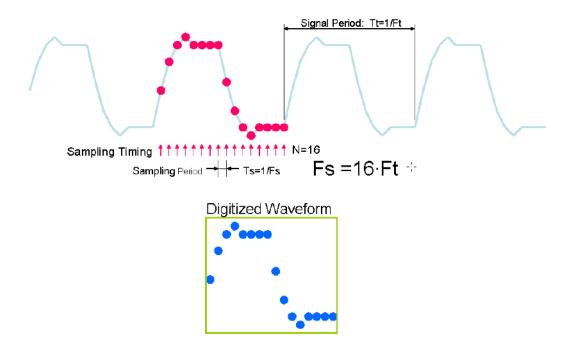

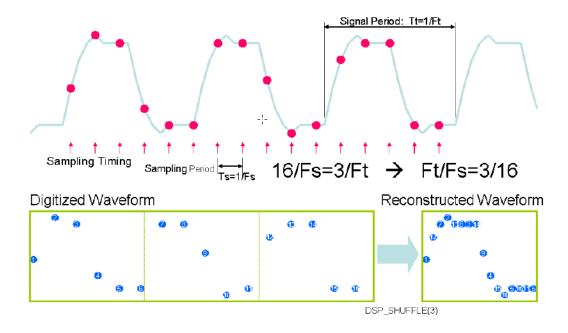

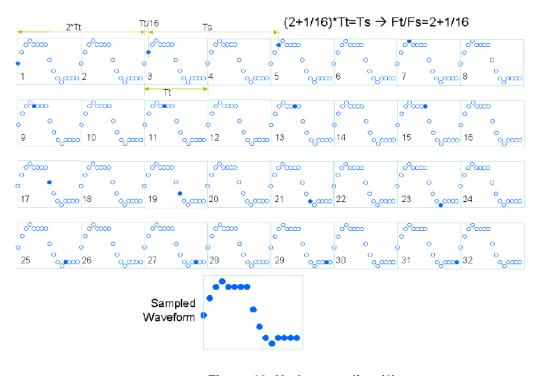

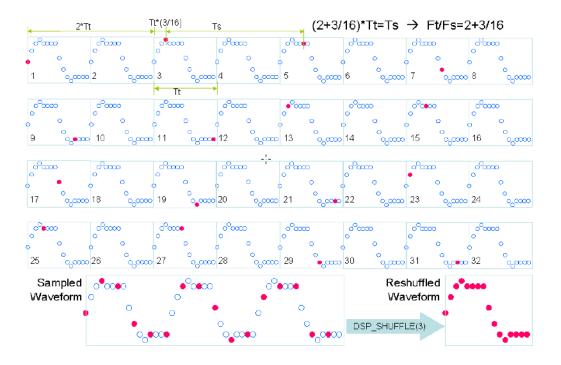

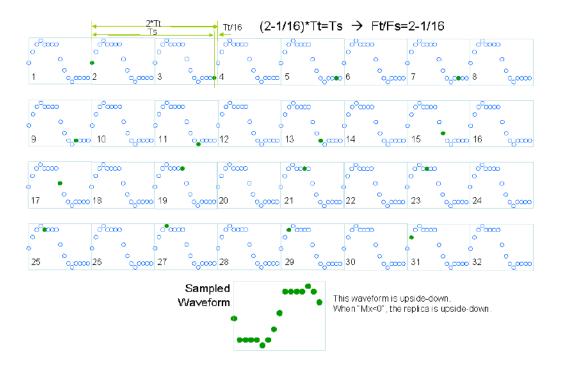

| Under-Sampling                                            | 162 |

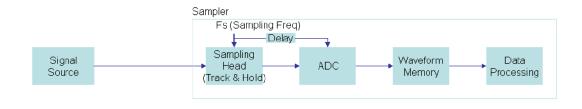

| Digitizer and Sampler                                     | 163 |

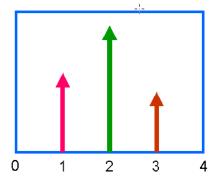

| Aliasing                                                  | 165 |

| Coherent Condition                                        | 168 |

| Waveform Reconstruction                                   | 170 |

| Index                                                     | 175 |

## About this Manual

The first part of this manual describes how to install and set up your DT9862 Series module and device driver, and verify that your module is working properly.

The second part of this manual describes the features of the DT9862 Series modules, the capabilities of the DT9862 Series Device Driver, and how to program the DT9862 Series modules using DT-Open Layers for .NET Class Library™ software. Troubleshooting information is also provided.

**Notes:** For more information on the class library, refer to the *DT-Open Layers for .NET Class Library User's Manual*. If you are using the DataAcq SDK or a software application to program your device, refer to the documentation for that software for more information.

The DT9862 Series modules are available either installed in a metal connection box with SMA connectors, or as board-level OEM versions that you can install in your own custom application.

#### **Intended Audience**

This document is intended for engineers, scientists, technicians, or others responsible for installing, setting up, using, and/or programming a DT9862 Series module for data acquisition operations.

It is assumed that you are familiar with the requirements of your application. It is also assumed that you have some familiarity with data acquisition principles, that you understand your application, and that you are familiar with the Microsoft<sup>®</sup> Windows Vista<sup>®</sup>, Windows 7, or Windows 8 operating system.

#### How this Manual is Organized

This manual is organized as follows:

- Chapter 1, "Overview," describes the major features of the DT9862 Series module, as well as the supported software and accessories for the module.

- Chapter 2, "Setting Up and Installing the Module," describes how to install a module, how to apply power to the module, and how to configure the device driver.

- Chapter 3, "Wiring Signals," describes how to wire signals to the DT9862 Series module.

- Chapter 4, "Verifying the Operation of a Module," describes how to verify the operation

of the module with the Quick DataAcq application.

- Chapter 5, "Principles of Operation," describes all of the features of the module and how to use them in your application.

- Chapter 6, "Supported Device Driver Capabilities," lists the data acquisition subsystems

and the associated features accessible using the DT9862 Series Device Driver.

- Chapter 7, "Troubleshooting," provides information that you can use to resolve problems with the module and device driver, should they occur.

- Chapter 8, "Calibration," describes how to calibrate the analog I/O circuitry of the module.

- Appendix A, "Specifications," lists the specifications of the DT9862 Series module.

- Appendix B, "Pin Assignments," describes the pin assignments of the connectors on the DT9862 Series module and STP78 screw terminal panel.

- Appendix C, "Ground, Power, and Isolation," describes the electrical characteristics of the DT9862 Series module.

- An index completes this manual.

#### **Conventions Used in this Manual**

The following conventions are used in this manual:

- Notes provide useful information that requires special emphasis, cautions provide information to help you avoid losing data or damaging your equipment, and warnings provide information to help you avoid catastrophic damage to yourself or your equipment.

- Items that you select or type are shown in **bold**.

- Courier font is used to represent source code.

#### **Related Information**

Refer to the following documents for more information on using the DT9862 Series module:

- Benefits of the Universal Serial Bus for Data Acquisition. This white paper describes why USB is an attractive alternative for data acquisition. It is available on the Data Translation® web site (www.datatranslation.com).

- *QuickDAQ User's Manual* (UM-24774). This manual describes how to create a QuickDAQ application to acquire and analyze data from a DT-Open Layers data acquisition module.

- DT-Open Layers for .NET User's Manual (UM-22161). For programmers who are developing their own application programs using Visual C# or Visual Basic .NET, this manual describes how to use the DT-Open Layers for .NET Class Library to access the capabilities of Data Translation data acquisition devices.

- DataAcq SDK User's Manual (UM-18326). For programmers who are developing their own application programs using the Microsoft C compiler, this manual describes how to use the DT-Open Layers™ DataAcq SDK™ to access the capabilities of Data Translation data acquisition devices. This manual is included on the Data Acquisition OMNI CD.

- LV-Link Online Help. This help file describes how to use LV-Link™ with the LabVIEW™ graphical programming language to access the capabilities of Data Translation data acquisition devices.

- DAQ Adaptor for MATLAB (UM-22024). This document describes how to use Data Translation's DAQ Adaptor to provide an interface between the MATLAB Data Acquisition subsystem from The MathWorks and Data Translation's DT-Open Layers architecture.

- Microsoft Windows Vista, Windows 7, or Windows 8 documentation.

- USB web site (http://www.usb.org).

#### Where To Get Help

Should you run into problems installing or using a DT9862 Series module, our Technical Support Department is available to provide technical assistance. Refer to Chapter 7 starting on page 113 for information on how to contact the Technical Support Department. If you are outside the U.S. or Canada, call your local distributor, whose number is listed on Data Translation's web site (www.datatranslation.com).

# Overview

| DT9862 Series Hardware Features | . 16 |

|---------------------------------|------|

| Supported Software              | . 18 |

| Accessories                     | 21   |

| Getting Started Procedure       | 22   |

#### DT9862 Series Hardware Features

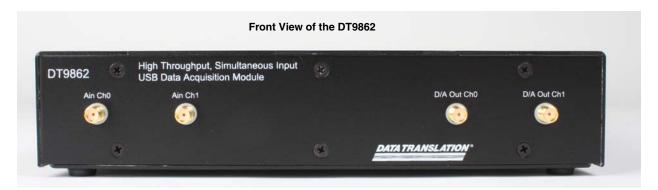

The DT9862 and DT9862S, shown in Figure 1, are high-speed, multifunction data acquisition modules for the USB (Ver. 2.0 or Ver. 1.1) bus.

Figure 1: DT9862 Series Module

The key hardware features of the DT9862 and DT9862S modules are as follows:

- Available installed in a metal connection box with SMA connectors, or as a board-level OEM version that you can install in your own custom application.

- Simultaneous operation of analog input, analog output, digital I/O, and counter/timer subsystems.

- Analog input subsystem:

- Two single-ended, simultaneous analog input channels.

- Throughput rate up to 10.0 MSamples/s when sampling one analog input channel,

5 MS/s when sampling two analog input channels, or 2 MS/s or less when sampling other combination of input channels.

- The DT9862 provides a bandwidth of 10 MHz. The DT9862S provides a bandwidth of 300 MHz (typical), which allows under-sampling.

- 16-bit A/D converters.

- Input range of ±2.5 V for the DT9862 and ±1.25 V for the DT9862S.

- A 13-location channel list.

- You can read the digital input port, two 32-bit counters, and three 32-bit quadrature decoders in the analog input data stream.

- Input samples are stored in memory on the module and are transferred in blocks to the host computer.

- Analog output subsystem:

- Up to two 16-bit D/A converters (if your module supports analog output channels).

- Output rate up to 2 MSamples/s (in small steps < 100 mV) or 500 kSamples/s per channel (simultaneous).

- Output range of ±2.5 V.

- The analog outputs are deglitched to prevent noise from interfering with the output signal.

- Output channel list. You can cycle through the output channel list using continuous output mode or waveform generation mode. Waveforms can hold from 2 to 128 kSamples for each analog output channel.

#### • Digital I/O subsystem:

- One digital input port, consisting of 16 digital input lines. You can program any of the

first eight digital input lines to perform interrupt-on-change operations. You can read

the value of the digital input port using the analog input channel-gain list.

- One digital output port, consisting of 16 digital output lines. You can output the value of the digital output port using the output channel list.

- Two 32-bit counter/timer (C/T) channels that perform event counting, up/down counting, frequency measurement, edge-to-edge measurement, continuous edge-to-edge measurement, continuous pulse output, one-shot, and repetitive one-shot operations. You can read the value of one or more of the C/T channels using the analog input channel list.

- Three 32-bit quadrature decoders that can provide relative or absolute position of quadrature encoder input and calculate rotational speed. You can read the value of one or more of the quadrature decoder channels using the analog input channel list.

- External or internal clock source.

- Trigger operations using a software command, an analog threshold value, or an external digital trigger.

- 500 V galvanic isolation barrier that prevents ground loops to maximize analog signal integrity and protect your computer.

## Supported Software

The following software is available for use with the DT9862 Series module and is on the Data Acquisition OMNI CD:

- DT9862 Series Device Driver The device driver allows you to use a DT9862 Series

module with any of the supported software packages or utilities. Refer to page 33 for

more information on configuring the device driver.

- Quick DataAcq application The Quick DataAcq application provides a quick way to get

up and running using a DT9862 Series module. Using this application, you can verify key

features of the module, display data on the screen, and save data to disk. Refer to Chapter

4 starting on page 55 for more information on using the Quick DataAcq application.

- QuickDAQ Base Version The base version of QuickDAQ is free-of-charge and allows

you to acquire and analyze data from all Data Translation USB and Ethernet devices,

except the DT9841 Series, DT9817, DT9835, and DT9853/54. Using the base version of

QuickDAQ, you can perform the following functions:

- Discover and select your devices.

- Configure all input channel settings for the attached sensors.

- Load/save multiple hardware configurations.

- Generate output stimuli (fixed waveforms, swept sine waves, or noise signals).

- On each supported data acquisition device, acquire data from all channels supported in the input channel list.

- Choose to acquire data continuously or for a specified duration.

- Choose software or triggered acquisition.

- Log acquired data to disk in an .hpf file.

- Display acquired data during acquisition in either a digital display using the Channel

Display window or as a waveform in the Channel Plot window.

- Choose linear or logarithmic scaling for the horizontal and vertical axes.

- View statistics about the acquired data, including the minimum, maximum, and mean values and the standard deviation in the Statistics window.

- Export time data to a .csv or .txt file; you can open the recorded data in Microsoft Excel® for further analysis.

- Read a previously recorded .hpf data file.

- Customize many aspects of the acquisition, display, and recording functions to suit your needs, including the acquisition duration, sampling frequency, trigger settings, filter type, and temperature units to use.

- QuickDAQ FFT Analysis Option When enabled with a purchased license key, the QuickDAQ FFT Analysis option includes all the features of the QuickDAQ Base version plus basic FFT analysis features, including the following:

- The ability to switch between the Data Logger time-based interface and the FFT Analyzer block/average-based interface.

- Supports software, freerun, or triggered acquisition with accept and reject controls for impact testing applications.

- Allows you to perform single-channel FFT (Fast Fourier Transform) operations, including AutoSpectrum, Spectrum, and Power Spectral Density, on the acquired analog input data. You can configure a number of parameters for the FFT, including the FFT size, windowing type, averaging type, integration type, and so on.

- Allows you to display frequency-domain data as amplitude or phase.

- Supports dB or linear scaling with RMS (root mean squared), peak, and peak-to-peak scaling options

- Supports linear or exponential averaging with RMS, vector, and peak hold averaging options.

- Supports windowed time channels.

- Supports the following response window types: Hanning, Hamming, Bartlett, Blackman, Blackman Harris, and Flat top.

- Supports the ability to lock the waveform output to the analysis frame time.

- Allows you to configure and view dynamic performance statistics, including the input below full-scale (IBF), total harmonic distortion (THD), spurious free dynamic range (SFDR), signal-to-noise and distortion ratio (SINAD), signal-to-noise ratio (SNR), and the effective number of bits (ENOB), for selected time-domain channels in the Statistics window.

- Supports digital IIR (infinite impulse response) filters.

- QuickDAQ Advanced FFT Analysis Option When enabled with a purchased software license, the QuickDAQ Advanced FFT Analysis option includes all the features of the QuickDAQ Base version with the FFT Analysis option plus advanced FFT analysis features, including the following:

- Allows you to designate a channel as a Reference or Response channel.

- Allows you to perform two-channel FFT analysis functions, including Frequency Response Functions (Inertance, Mobility, Compliance, Apparent Mass, Impedance, Dynamic Stiffness, or custom FRF) with H1, H2, or H3 estimator types, Cross-Spectrum, Cross Power Spectral Density, Coherence, and Coherent Output Power.

- Supports the Exponential response window type.

- Supports the following reference window types: Hanning, Hamming, Bartlett,

Blackman, Blackman Harris, FlatTop, Exponential, Force, and Cosine Taper windows.

- Supports real, imaginary, and Nyquist display functions.

- Allows you to save data in the .uff file format.

- DT-Open Layers for .NET Class Library Use this class library if you want to use Visual C# or Visual Basic for .NET to develop your own application software for a DT9862 Series module using Visual Studio 2003 to 2012; the class library complies with the DT-Open Layers standard.

- DataAcq SDK Use the Data Acq SDK if you want to use Visual Studio 6.0 and Microsoft

C or C++ to develop your own application software for a DT9862 Series module using

Windows Vista, Windows 7, or Windows 8; the DataAcq SDK complies with the DT-Open

Layers standard.

- DAQ Adaptor for MATLAB Data Translation's DAQ Adaptor provides an interface between the MATLAB Data Acquisition (DAQ) subsystem from The MathWorks and Data Translation's DT-Open Layers architecture.

- LV-Link A link to LV-Link is included on the Data Acquisition OMNI CD. Use LV-Link if you want to use the LabVIEW graphical programming language to access the capabilities of Data Translation modules.

Refer to the Data Translation web site (www.datatranslation.com) for information about selecting the right software package for your needs.

# Accessories

Table 1 lists the following optional accessories for use with the DT9862 Series modules.

Table 1: Accessories for the DT9862 Series Module

|       | Accessory | Description                                                                                                                                                             |

|-------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STP78 |           | Screw terminal panel for connecting digital signals to the DT9862 Series module. Use this panel with the EP390 cable.                                                   |

| EP390 |           | A 1.52 meter cable with two 78-pin connectors that connect the STP78 screw terminal panel to the DT9862 Series module.                                                  |

| EP361 |           | +5 V power supply and cable. EP361 is shipped with the standard version of the DT9862 Series module. If you purchased the OEM version of the module, EP361 is optional. |

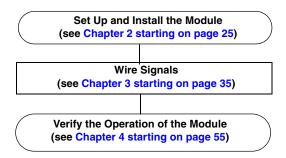

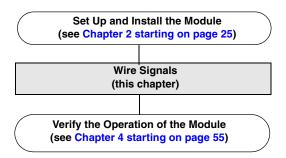

# **Getting Started Procedure**

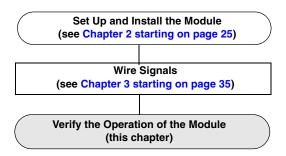

The flow diagram shown in Figure 2 illustrates the steps needed to get started using the DT9862 Series module. This diagram is repeated in each Getting Started chapter; the shaded area in the diagram shows you where you are in the procedure.

Figure 2: Getting Started Flow Diagram

# Part 1: Getting Started

# Setting Up and Installing the Module

| Unpacking                                   | . 27 |

|---------------------------------------------|------|

| System Requirements                         | . 28 |

| Applying Power to the Module                | . 29 |

| Attaching Modules to the Computer           | . 30 |

| Configuring the DT9862 Series Device Driver | . 33 |

**Note:** DT9862 Series modules are factory-calibrated. If you decide that you want to recalibrate the analog input or analog output circuitry, refer to the instructions in Chapter 8.

# Unpacking

Open the shipping box and verify that the following items are present:

- DT9862 Series module

- Data Acquisition OMNI CD

- USB cable

- EP361 power supply and power cable

**Note:** If you purchased the OEM version of the DT9862 Series, the USB cable and EP361 power supply and cable are not shipped with the module.

If an item is missing or damaged, contact Data Translation. If you are in the United States, call the Customer Service Department at (508) 481-3700, ext. 1323. An application engineer will guide you through the appropriate steps for replacing missing or damaged items. If you are located outside the United States, call your local distributor, listed on Data Translation's web site (www.datatranslation.com).

# System Requirements

For reliable operation, ensure that your computer meets the following system requirements:

- Processor: Pentium 4/M or equivalent

- RAM: 1 GB

- Screen Resolution: 1024 x 768 pixels

- Operating System: Windows 8, Windows 7, or Windows Vista (32- and 64-bit)

- Disk Space: 4 GB

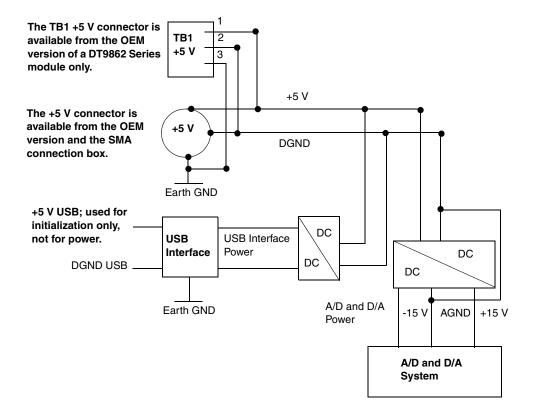

## Applying Power to the Module

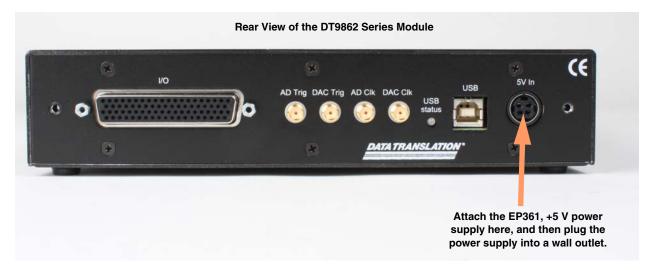

The standard DT9862 and DT9862S modules are shipped with an EP361 +5V power supply and cable. For the OEM version of the DT9862 and DT9862S modules, you must provide your own +5 V power source or purchase the EP361 power supply and cable from Data Translation.

To apply power to the module, do the following:

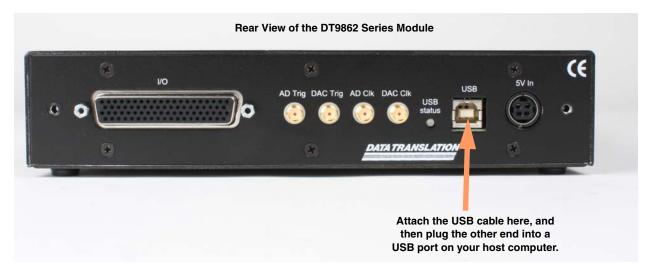

1. Connect the +5 V power supply to the power connector on the DT9862 or DT9862S module. Refer to Figure 3.

Figure 3: Attaching a +5 V Power Supply to the DT9862 Series Module

**2.** Plug the power supply into a wall outlet.

For more detailed information about ground, power, and isolation connections on a DT9862 Series module, refer to Appendix C starting on page 149.

## Attaching Modules to the Computer

This section describes how to attach DT9862 Series modules to the host computer.

**Note:** Most computers have several USB ports that allow direct connection to USB devices. If your application requires more DT9862 Series modules than you have USB ports for, you can expand the number of USB devices attached to a single USB port by using expansion hubs. For more information, refer to page 31.

You can unplug a module, then plug it in again, if you wish, without causing damage. This process is called hot-swapping. Your application may take a few seconds to recognize a module once it is plugged back in.

You must install the device driver before connecting your DT9862 Series module(s) to the host computer. Run the installation program on your Data Acquisition OMNI CD to install the device driver and other software for the module.

#### **Connecting Directly to the USB Ports**

To connect a DT9862 Series module directly to a USB port on your computer, do the following:

- 1. Make sure that you have attached a power supply to the module.

- 2. Attach one end of the USB cable to the USB port on the module.

- **3.** Attach the other end of the USB cable to one of the USB ports on the host computer, as shown in Figure 4.

The operating system automatically detects the USB module and starts the Found New Hardware wizard.

Figure 4: Attaching the USB Cable to the DT9862 Series Module

#### **4.** For Windows Vista:

a. Click Locate and install driver software (recommended).

The popup message "Windows needs your permission to continue" appears.

b. Click Continue.

The Windows Security dialog box appears.

c. Click Install this driver software anyway.

The LED on the module turns green.

**Note:** Windows 7 and Windows 8 find the device automatically.

**5.** Repeat these steps to attach another DT9862 Series module to the host computer, if desired.

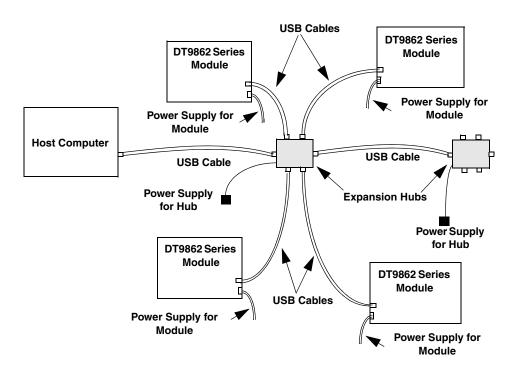

### **Connecting to an Expansion Hub**

Expansion hubs are powered by their own external power supply. The practical number of DT9862 Series modules that you can connect to a single USB port depends on the throughput you want to achieve.

To connect multiple DT9862 Series modules to an expansion hub, do the following:

- 1. Make sure that you have attached a power supply to the module.

- **2.** Attach one end of the USB cable to the module and the other end of the USB cable to an expansion hub.

- 3. Connect the power supply for the expansion hub to an external power supply.

- **4.** Connect the expansion hub to the USB port on the host computer using another USB cable.

The operating system automatically detects the USB module and starts the Found New Hardware wizard.

- 5. For Windows Vista:

- a. Click Locate and install driver software (recommended).

The popup message "Windows needs your permission to continue" appears.

b. Click Continue.

The Windows Security dialog box appears.

c. Click Install this driver software anyway.

The LED on the module turns green.

**Note:** Windows 7 and Windows 8 find the device automatically.

**6.** Repeat these steps until you have attached the number of expansion hubs and modules that you require. Refer to Figure 5.

The operating system automatically detects the USB devices as they are installed.

Figure 5: Attaching Multiple Modules Using Expansion Hubs

## Configuring the DT9862 Series Device Driver

**Note:** In Windows 7, Windows 8, and Vista, you must have administrator privileges to run the Open Layers Control Panel. When you double-click the Open Layers Control Panel icon, you may see the Program Compatibility Assistant. If you do, select **Open the control panel using recommended settings**. You may also see a Windows message asking you if you want to run the Open Layers Control Panel as a "legacy CPL elevated." If you get this message, click **Yes**.

If you do not get this message and have trouble making changes in the Open Layers Control Panel, right click the DTOLCPL.CPL file and select **Run as administrator**. By default, this file is installed in the following location:

Windows 7, Windows 8, and Vista (32-bit)

C:\Windows\System32\Dtolcpl.cpl

Windows 7, Windows 8, and Vista (64-bit)

C:\Windows\SysWOW64\Dtolcpl.cpl

To configure the device driver for the DT9862 Series modules, do the following:

- 1. If you have not already done so, power up the host computer and all peripherals.

- 2. From the Windows Start menu, select Settings | Control Panel.

- **3.** From the Control Panel, double-click **Open Layers Control Panel**. *The Data Acquisition Control Panel dialog box appears*.

- **4.** Click the DT9862 Series module that you want to configure, and then click **Advanced**. *The Configurable Board Options dialog box appears*.

- 5. If required, select the digital input line(s) that you want to use for interrupt-on-change operations. When any of the selected lines changes state, the module reads the entire digital input value and generates an interrupt.

- 6. If you are using USB 2.0, check the USB Version 2.0 checkbox to improve performance.

- 7. If you want to use the internal  $50~\Omega$  termination that the DT9862 module provides to match the impedance of your cable, check the **Channel 0** checkbox to use the internal termination on analog input channel 0 and/or check the **Channel 1** checkbox to use the internal termination on analog input channel 1. Refer to page 37 for more information on cable matching.

**Note:** You can also change this setting programmatically, if desired, by writing to a register on the module; refer to page 153 for more information.

The DT9862S does not provide 50  $\Omega$  of termination on the inputs; therefore, you must provide your own external termination at the end of the cable. Refer to page 37 for more information on cable matching.

- 8. Click OK.

- 9. If you want to rename the module, click Edit Name, enter a new name for the module, and then click OK. The name is used to identify the module in all subsequent applications.

- **10.** Repeat steps 4 to 9 for the other modules that you want to configure.

- **11.** When you are finished configuring the modules, click **Close**.

Continue with the instructions on wiring in Chapter 3.

# Wiring Signals

| Preparing to Wire Signals           | . 37 |

|-------------------------------------|------|

| Wiring Analog Input Signals         | . 40 |

| Wiring Analog Output Signals        | . 41 |

| Wiring Signals to the I/O Connector | . 46 |

# Preparing to Wire Signals

This section provides recommendations and information about wiring signals to the DT9862 Series module.

#### **Wiring Recommendations**

Keep the following recommendations in mind when wiring signals to the DT9862 Series module:

- Follow standard ESD procedures when wiring signals to the module.

- Separate power and signal lines by using physically different wiring paths or conduits.

- To avoid noise, do not locate the box and cabling next to sources that produce high

electromagnetic fields, such as large electric motors, power lines, solenoids, and electric

arcs, unless the signals are enclosed in a mumetal shield.

- Prevent electrostatic discharge to the I/O while the box is operational.

- Connect all unused analog input channels to analog ground.

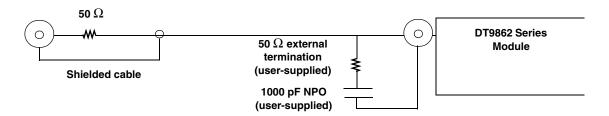

#### **High-Performance Considerations**

Cables have a characteristic impedance that must be matched or amplitude and phase errors will result in poor data. For optimal performance, particularly at high frequencies, do the following:

- Pay attention to cable matching from the source to the analog input channels of the DT9862 Series module.

- Place a resistor with the same impedance in series with the cable at your source.

- Add termination with matched impedance at the module.

The DT9862 provides  $50 \Omega$  of internal termination that you can select for each analog input channel using the Control Panel applet; refer to page 33 for more information. Alternatively, you can provide your own external termination.

The DT9862 does not provide 50  $\Omega$  of input termination; therefore, you must provide your own external termination at the end of the cable (use a T connector to do this).

At frequencies of 10 MHz and above, connect the shield all the way through.

The following example assumes that your cable has an impedance of 50  $\Omega$ . You can place a 50  $\Omega$  resistor in series with a 1000 pF NPO capacitor to common, as shown in Figure 6. This will provide high frequency matching without DC loading of the termination resistor.

Figure 6: Example of Cable Matching

#### **Layout of the DT9862 Series Module**

The DT9862 Series module contains SMA connectors and a 78-pin, I/O connector for connecting digital I/O, counter/timer, and quadrature decoder signals. Figure 7 shows the I/O connectors on the front of the DT9862 Series module, and Figure 8 shows the I/O connectors on the rear of the DT9862 Series module.

Figure 7: I/O Connectors on the Front of the DT9862 Series Module

Figure 8: I/O Connectors on the Rear of the DT9862 Series Module

You can wire the following I/O signals to the DT9862 Series module:

- **Analog input signals** Wire analog input signals using the SMA connectors labelled Ain Ch0 and Ain Ch1.

- **Analog output signals** Wire analog output signals using the SMA connectors labelled D/A Out Ch0 and D/A Out Ch1.

- **Digital I/O signals** To wire digital I/O signals, you must use the appropriate pins on the I/O connector on the DT9862 Series module. You can access the pins by using the STP78 screw terminal panel and EP390 cable or by building your own cable/panel. Refer to page 146 for connector pin assignments.

- Counter/timer signals To wire counter/timer signals, you must use the appropriate pins on the I/O connector on the DT9862 Series module. You can access the pins by using the STP78 screw terminal panel and EP390 cable or by building your own cable/panel. Refer to page 146 for connector pin assignments.

- External A/D clock or trigger signal You can wire external clock/trigger signals for the analog input subsystem using the SMA connectors labelled AD Clk for A/D clock signals and AD Trig for A/D trigger signals.

- External D/A clock or trigger signal You can wire external clock/trigger signals for the

analog output subsystem using the SMA connectors labelled DAC Clk for D/A clock

signals and DAC Trig for D/A trigger signals.

The following sections describe how to wire signals to a DT9862 Series module.

# Wiring Analog Input Signals

The DT9862 Series supports voltage inputs. You can connect analog input signals to the DT9862 Series modules in **single-ended** mode. In this mode, the source of the input should be close to the module; all the input signals are referred to the same common ground.

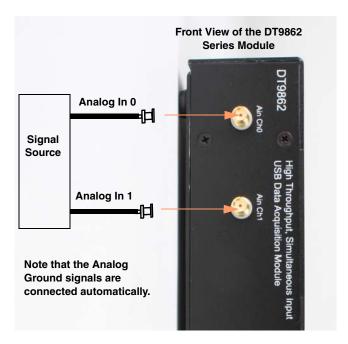

Figure 9 shows how to connect voltage inputs (channels 0 and 1, in this case) to the SMA connectors on a DT9862 Series module.

Figure 9: Wiring Analog Inputs to a DT9862 Series Module

# Wiring Analog Output Signals

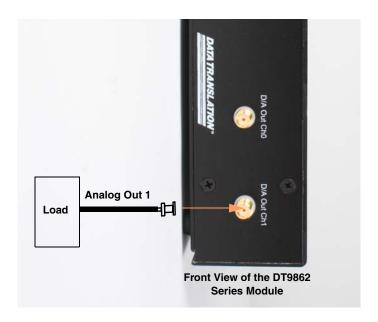

Figure 10 shows how to connect an analog output voltage signal (channel 1, in this case) to the SMA connector on a DT9862 Series module.

Figure 10: Wiring Analog Outputs to a DT9862 Series Module

# Wiring Signals to the I/O Connector

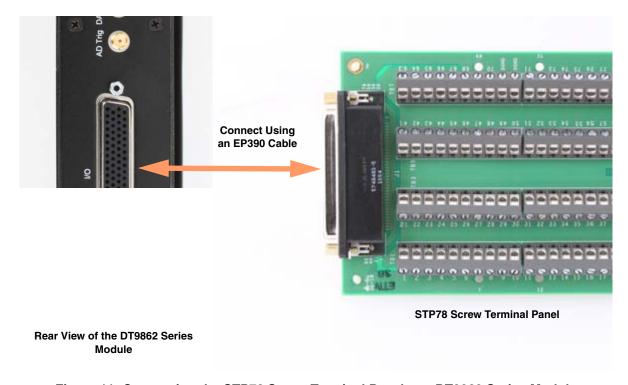

If want to connect digital, counter/timer, or quadrature decoder signals to a DT9862 Series module, it is recommended that you connect an STP78 screw terminal panel to the 78-pin, D-sub, I/O connector on the module. Alternatively, you can build your own screw terminal panel and cable.

Figure 11 shows how to connect the STP78 screw terminal panel to the I/O connector using the EP390 cable.

Figure 11: Connecting the STP78 Screw Terminal Panel to a DT9862 Series Module

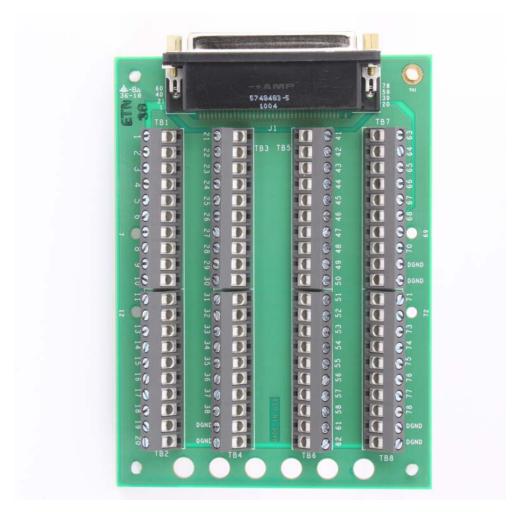

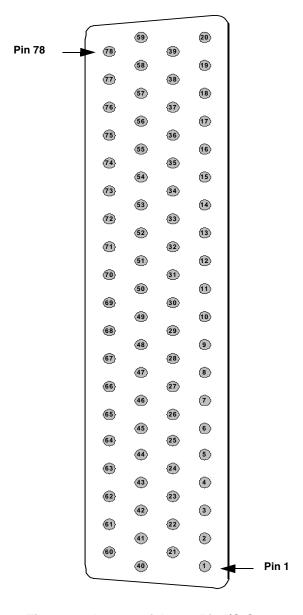

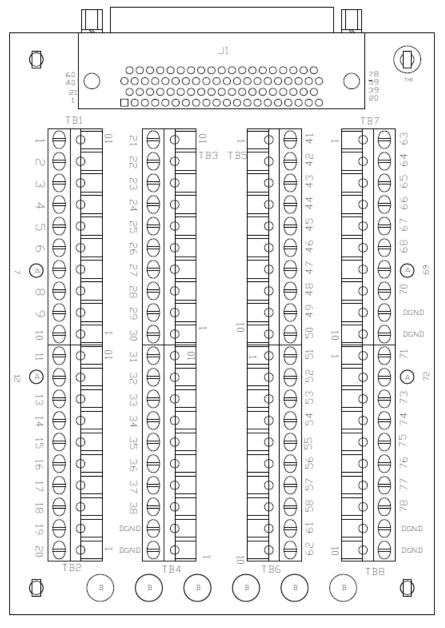

Figure 12 shows the screw terminal designations for the STP78 screw terminal panel.

Figure 12: Layout of the STP78

Table 2 lists the assignments for each screw terminal on the STP78 screw terminal panel.

**Table 2: Screw Terminal Assignments for the STP78 Screw Terminal Panel**

| Screw<br>Terminal | Terminal Block<br>Position | Signal Description | Screw<br>Terminal | Terminal<br>Block Position | Signal Description |

|-------------------|----------------------------|--------------------|-------------------|----------------------------|--------------------|

| 1                 | TB1, 10                    | Quad Dec 1 Index   | 41                | TB5, 1                     | Digital Output 0   |

| 2                 | TB1, 9                     | Digital Ground     | 42                | TB5, 2                     | Digital Output 1   |

| 3                 | TB1, 8                     | Quad Dec 1 B       | 43                | TB5, 3                     | Digital Output 2   |

| 4                 | TB1, 7                     | Digital Ground     | 44                | TB5, 4                     | Digital Output 3   |

| 5                 | TB1, 6                     | Quad Dec 1 A       | 45                | TB5, 5                     | Digital Output 4   |

| 6                 | TB1, 5                     | Digital Ground     | 46                | TB5, 6                     | Digital Output 5   |

| 7                 | TB1, 4                     | Quad Dec 0 Index   | 47                | TB5, 7                     | Digital Output 6   |

| 8                 | TB1, 3                     | Digital Ground     | 48                | TB5, 8                     | Digital Output 7   |

| 9                 | TB1, 2                     | Quad Dec 0 B       | 49                | TB5, 9                     | Digital Output 8   |

| 10                | TB1, 1                     | Digital Ground     | 50                | TB5, 10                    | Digital Output 9   |

| 11                | TB2, 10                    | Quad Dec 0 A       | 51                | TB6, 1                     | Digital Output 10  |

| 12                | TB2, 9                     | Digital Ground     | 52                | TB6, 2                     | Digital Output 11  |

| 13                | TB2, 8                     | Counter 0 Out      | 53                | TB6, 3                     | Digital Output 12  |

| 14                | TB2, 7                     | Digital Ground     | 54                | TB6, 4                     | Digital Output 13  |

| 15                | TB2, 6                     | Counter 0 Gate     | 55                | TB6, 5                     | Digital Output 14  |

| 16                | TB2, 5                     | Digital Ground     | 56                | TB6, 6                     | Digital Output 15  |

| 17                | TB2, 4                     | Counter 0 Clock    | 57                | TB6, 7                     | Digital Ground     |

| 18                | TB2, 3                     | Digital Ground     | 58                | TB6, 8                     | Digital Ground     |

| 19                | TB2, 2                     | +5 V Output        | 59                | TB6, 9                     | Digital Input 0    |

| 20                | TB2, 1                     | +5 V Output Ground | 60                | TB6, 10                    | Digital Input 1    |

| 21                | TB3, 10                    | Quad Dec 2 Index   | 61                | TB7, 1                     | Digital Input 2    |

| 22                | TB3, 9                     | Digital Ground     | 62                | TB7, 2                     | Digital Input 3    |

| 23                | TB3, 8                     | Quad Dec 2 B       | 63                | TB7, 3                     | Digital Input 4    |

| 24                | TB3, 7                     | Digital Ground     | 64                | TB7, 4                     | Digital Input 5    |

| 25                | TB3, 6                     | Quad Dec 2 A       | 65                | TB7, 5                     | Digital Input 6    |

| 26                | TB3, 5                     | Digital Ground     | 66                | TB7, 6                     | Digital Input 7    |

| 27                | TB3, 4                     | Counter 1 Output   | 67                | TB7, 7                     | Digital Input 8    |

| 28                | TB3, 3                     | Digital Ground     | 68                | TB7, 8                     | Digital Input 9    |

| 29                | TB3, 2                     | Counter 1 Gate     | 69                | TB7, 9                     | Digital Ground     |

| 30                | TB3, 1                     | Digital Ground     | 70                | TB7, 10                    | Digital Ground     |

Table 2: Screw Terminal Assignments for the STP78 Screw Terminal Panel (cont.)

| Screw<br>Terminal | Terminal Block<br>Position | Signal Description | Screw<br>Terminal | Terminal<br>Block Position | Signal Description |

|-------------------|----------------------------|--------------------|-------------------|----------------------------|--------------------|

| 31                | TB4, 10                    | Counter 1 Clock    | 71                | TB8, 1                     | Digital Input 10   |

| 32                | TB4, 9                     | Digital Ground     | 72                | TB8, 2                     | Digital Input 11   |

| 33                | TB4, 8                     | Reserved           | 73                | TB8, 3                     | Digital Input 12   |

| 34                | TB4, 7                     | Reserved           | 74                | TB8, 4                     | Digital Input 13   |

| 35                | TB4, 6                     | Reserved           | 75                | TB8, 5                     | Digital Input 14   |

| 36                | TB4, 5                     | Reserved           | 76                | TB8, 6                     | Digital Input 15   |

| 37                | TB4, 4                     | Reserved           | 77                | TB8, 7                     | Digital Ground     |

| 38                | TB4, 3                     | Reserved           | 78                | TB8, 8                     | Digital Ground     |

| 39                | TB4, 2                     | Digital Ground     | 79                | TB8, 9                     | Digital Ground     |

| 40                | TB4, 1                     | Digital Ground     | 80                | TB8, 10                    | Digital Ground     |

The following subsections describe how to connect digital I/O, counter/timer, and quadrature decoder signals to the STP78 screw terminal panel.

# Wiring Digital I/O Signals

Figure 13 shows how to connect digital input signals (lines 0 and 1, in this case) to the STP78 screw terminal panel.

# Digital Ground Digital Input 0 Digital Input 1 Digital Input 1

Figure 13: Wiring Digital Inputs to the STP78 Screw Terminal Panel

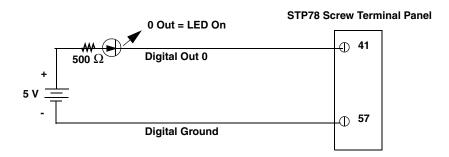

Figure 14 shows how to connect a digital output (line 0, in this case) to the digital output pins of the I/O connector.

Figure 14: Wiring Digital Outputs to the STP78 Screw Terminal Panel

# Wiring Counter/Timer Signals

The DT9862 Series module provides two counter/timer channels that you can use for the following operations:

- · Event counting

- Up/down counting

- Frequency measurement

- Pulse width/period measurement

- Edge-to-edge measurement

- Continuous edge-to-edge measurement

- Pulse output (continuous, one-shot, and repetitive one-shot)

This section describes how to connect counter/timer signals to the STP78 screw terminal panel. Refer to Chapter 5 for more information about using the counter/timers. Refer to page 146 for more information about the STP78 screw terminal panel.

#### **Event Counting**

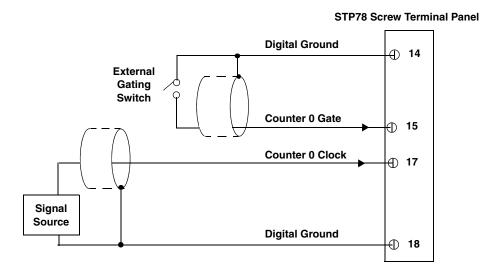

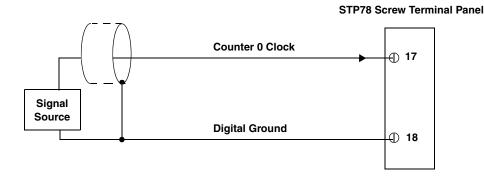

Figure 15 shows how to connect counter/timer signals to perform an event counting operation on counter/timer 0 using an external gate.

The counter counts the number of rising edges that occur on the Counter 0 Clock input when the Counter 0 Gate signal is in the active state (as specified by software). Refer to page 47 for more information on event counting operations.

Figure 15: Wiring Counter/Timer Signals to the STP78 Screw Terminal Panel for an Event Counting Operation Using an External Gate

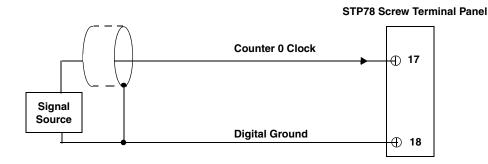

Figure 16 shows how to connect counter/timer signals to perform an event counting operation on counter/timer 0 without using a gate. The counter counts the number of rising edges that occur on the Counter 0 Clock input.

Figure 16: Wiring Counter/Timer Signals to the STP78 Screw Terminal Panel for an Event Counting Operation Without Using a Gate

#### **Up/Down Counting**

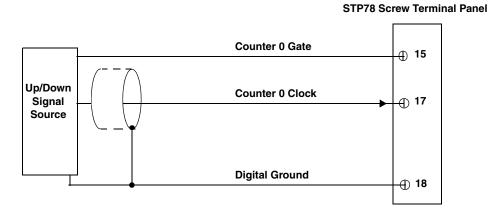

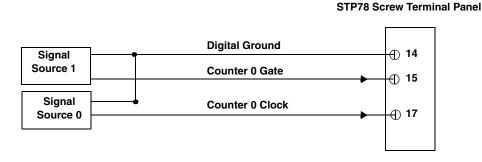

Figure 17 shows how to connect counter/timer signals to perform an up/down counting operation on counter/timer 0. The counter keeps track of the number of rising edges that occur on the Counter 0 Clock input. The counter increments when the Counter 0 Gate signal is high and decrements when the Counter 0 Gate signal is low. Refer to page 91 for more information about up/down counting operations.

Figure 17: Wiring Counter/Timer Signals to the STP78 Screw Terminal Panel for an Up/Down Counting Operation

#### Frequency Measurement

One way to measure frequency is to connect a pulse of a known duration (such as a one-shot output of counter/timer 1) to the Counter 0 Gate input.

Figure 18 shows how to connect counter/timer signals to perform a frequency measurement operation. In this case, the frequency of the Counter 0 clock input is the number of counts divided by the period of the Counter 0 Gate input signal. Refer to page 91 for more information about frequency measurement operations.

# Counter 1 Out Counter 0 Gate 13 Counter 0 Gate 17 Signal Source Digital Ground 18

Figure 18: Wiring Counter/Timer Signals to the STP78 Screw Terminal Panel for a Frequency Measurement Operation Using an External Pulse

#### Period/Pulse Width Measurement

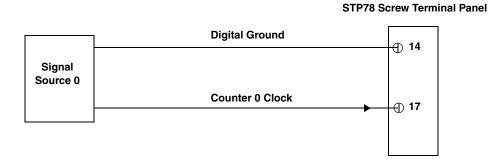

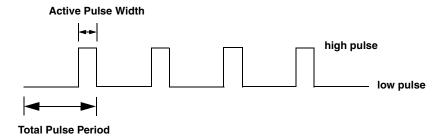

Figure 19 shows how to connect counter/timer signals to perform a period/pulse width measurement operation on counter/timer 0. You specify the active pulse (high or low) in software. The pulse width is the percentage of the total pulse period that is active. Refer to page 90 for more information about pulse periods and pulse widths.

Figure 19: Wiring Counter/Timer Signals to the STP78 Screw Terminal Panel for a Period/Pulse Width Measurement Operation

#### Edge-to-Edge Measurement

Figure 20 shows how to connect counter/timer signals to perform an edge-to-edge measurement operation using two signal sources. The counter measures the number of counts between the start edge (in this case, a rising edge on the Counter 0 Clock signal) and the stop edge (in this case, a falling edge on the Counter 0 Gate signal).

You specify the start edge and the stop edge in software. Refer to page 92 for more information on edge-to-edge measurement mode.

Figure 20: Wiring Counter/Timer Signals to the STP78 Screw Terminal Panel for an Edge-to-Edge Measurement Operation

#### Continuous Edge-to-Edge Measurement

Figure 21 shows how to connect counter/timer signals to perform a continuous edge-to-edge measurement operation. The counter measures the number of counts between two consecutive start edges (in this case, a rising edge on the Counter 0 Clock signal).

You specify the start edge in software. Refer to page 93 for more information on continuous edge-to-edge measurement operations.

Figure 21: Wiring Counter/Timer Signals to the STP78 Screw Terminal Panel for a Continuous Edge-to-Edge Measurement Operation

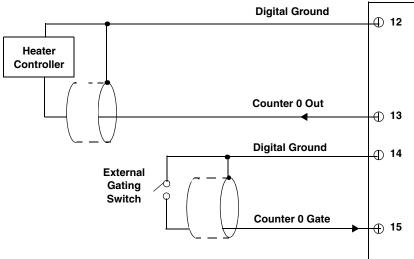

#### Pulse Output

Figure 22 shows how to connect counter/timer signals to perform a pulse output operation on counter/timer 0; in this example, an external gate is used. Refer to page 52 for more information on pulse output operations.

# STP78 Screw Terminal Panel

Figure 22: Wiring Counter/Timer Signals to the STP78 Screw Terminal Panel for a Pulse Output Operation Using an External Gate

# **Wiring Quadrature Decoder Signals**

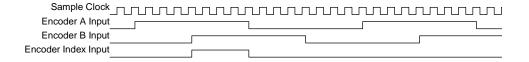

The DT9862 Series modules provide three quadrature decoder channels that allow simultaneous decoding of three quadrature encoded inputs.

Each quadrature decoder supports "A," "B," and "Index" inputs and is used to interface with a quadrature encoder sensor. The A and B input relationships are used to increment or decrement the positional count; the Index input can be used to zero-out the positional count. Refer to page 96 for more information about using the quadrature decoders.

Figure 23 shows how to connect signals from a quadrature encoder to quadrature decoder 0 on the STP78 screw terminal panel.

**STP78 Screw Terminal Panel**

# Quadrature Encoder Quad Dec 0 Index Quad Dec 0 B Quad Dec 0 A Digital Ground 12

Figure 23: Wiring Quadrature Decoder Signals to the STP78 Screw Terminal Panel

# Verifying the Operation of a Module

| Running the Quick DataAcq Application | 57 |

|---------------------------------------|----|

| Testing Single-Value Analog Input     | 58 |

| Testing Single-Value Analog Output    | 59 |

| Testing Continuous Analog Input       | 60 |

| Testing Single-Value Digital Input    | 61 |

| Testing Single-Value Digital Output   | 62 |

| Testing Frequency Measurement         | 63 |

| Testing Pulse Output                  | 64 |

You can verify the operation of a DT9862 Series module using the Quick DataAcq application. Quick DataAcq lets you do the following:

- Acquire data from a single analog input channel or digital input port

- Acquire data continuously from one or more analog input channels using an oscilloscope, strip chart, or Fast Fourier Transform (FFT) view

- Measure the frequency of events

- Output data from a single analog output channel or digital output port

- Output pulses either continuously or as a one-shot

- Save the input data to disk

# Running the Quick DataAcq Application

The Quick DataAcq application is installed automatically when you install the driver software.

To run the Quick DataAcq application, do the following:

- 1. If you have not already done so, power up your computer and any attached peripherals.

- 2. Click Start from the Task Bar.

- 3. Browse to Programs | Data Translation, Inc | DT-Open Layers for Win32 | QuickDataAcq.

The main menu appears.

**Note:** The Quick DataAcq application allows you to verify basic operations on the module; however, it may not support all of the module's features.

For information on each of the features provided, use the online help for the Quick DataAcq application by pressing F1 from any view or selecting the **Help** menu. If the system has trouble finding the help file, navigate to C:\Program Files\Data Translation\Win32\ dtdataacq.hlp, where C: is the letter of your hard disk drive.

# Testing Single-Value Analog Input

To verify that the module can read a single analog input value, do the following:

- **1.** Connect a voltage source, such as a function generator, to analog input channel 0 on the DT9862 Series module. Refer to page 40 for an example of how to connect an analog input.

- **2.** In the Quick DataAcq application, choose **Single Analog Input** from the **Acquisition** menu.

- 3. Select the appropriate DT9862 Series module from the **Board** list box.

- **4.** In the **Channel** list box, select analog input channel 0.

- **5.** In the **Range** list box, select the range for the channel.

- 6. Select Single Ended.

- 7. Click **Get** to acquire a single value from analog input channel 0. *The application displays the value on the screen in both text and graphical form.*

# Testing Single-Value Analog Output

To verify that the module can output a single analog output value, do the following:

- 1. Connect an oscilloscope or voltmeter to analog output channel 0 on the module. Refer to page 41 for an example of how to connect analog output signals.

- 2. In the Quick DataAcq application, choose Single Analog Output from the Control menu.

- 3. Select the appropriate DT9862 Series module from the **Board** list box.

- **4.** In the **Channel** list box, select analog output channel 0.

- **5.** In the **Range** list box, select the output range of DAC0.

- **6.** Enter an output value, or use the slider to select a value, to output from DAC0.

- 7. Click **Send** to output a single value from analog output channel 0. *The application displays the output value both on the slider and in the text box.*

# Testing Continuous Analog Input

To verify that the module can perform a continuous analog input operation, do the following:

- 1. Connect known voltage sources, such as the outputs of a function generator, to analog input channels 0 and 1 on the DT9862 Series module.

- **2.** In the Quick DataAcq application, choose **Scope** from the **Acquisition** menu.

- **3.** Select the DT9862 Series module from the **Board** list box.

- **4.** In the **Sec/Div** list box, select the number of seconds per division (.1 to .00001) for the display.

- **5.** In the **Channel** list box, select analog input channel 1, and then click **Add** to add the channel to the channel list. *Note that, by default, channel 0 is included in the channel list.*

- **6.** Click **Config** from the Toolbar.

- 7. In the Config dialog, select ChannelType, and then select Single Ended.

- 8. In the Config dialog, select Range, and then select Bipolar.

- 9. Click **OK** to close the dialog box.

- **10.** In the **Trigger** box, select **Auto** to acquire data continuously from the specified channels or **Manual** to acquire a burst of data from the specified channels.

- **11.** Click **Start** from the Toolbar to start the continuous analog input operation. *The application displays the values acquired from each channel in a unique color on the oscilloscope view.*

- **12.** Click **Stop** from the Toolbar to stop the operation.

# Testing Single-Value Digital Input

To verify that the module can read a single digital input value, do the following:

- 1. Connect a digital input to digital input line 0 on the DT9862 Series module. Refer to page 46 for information about how to connect a digital input.

- 2. In the Quick DataAcq application, choose **Digital Input** from the **Acquisition** menu.

- 3. Select the appropriate DT9862 Series module from the **Board** list box.

- 4. Click Get.

The application displays the entire 16-bit digital input value (0 to FFFF) in both the Data box and the Digital Input box.

In addition, application shows the state of the lower eight digital input lines (lines 0 to 7) in the graphical display. If an indicator light is lit (red), the line is high; if an indicator light is not lit (black), the line is low.

**Note:** Although the DT9862 Series module contains 16 digital input lines, the Quick DataAcq application shows indicator lights for the lower eight digital input lines only. The 16-bit value is the correct value for all 16 lines.

# Testing Single-Value Digital Output

**Note:** Although the DT9862 Series modules contain 16 digital output lines, the Quick DataAcq application allows you to perform a digital output operation on the lower eight digital output lines (lines 0 to 7) only.

To verify that the module can output a single digital output value, do the following:

- 1. Connect a digital output to digital output line 0 on the DT9862 Series module. Refer to page 46 for information about how to connect a digital output.

- 2. In the Quick DataAcq application, choose **Digital Output** from the **Control** menu.

- 3. Select the appropriate DT9862 Series module from the Board list box.

- 4. Click the appropriate indicator lights to select the types of signals to write from the digital output lines. If you select a light, the module outputs a high-level signal; if you do not select a light, the module outputs a low-level signal. You can also enter an output value for the lower eight digital output lines (0 to FF) in the Hex text box.

- 5. Click Send.

The values of the lower eight digital output lines are output appropriately.

# **Testing Frequency Measurement**

To verify that the module can perform a frequency measurement operation, do the following:

1. Wire an external clock source to counter/timer 0 on the DT9862 Series module. Refer to page 49 for an example of how to connect an external clock.

**Note:** The Quick DataAcq application works only with counter/timer 0.

- **2.** In the Quick DataAcq application, choose **Measure Frequency** from the **Acquisition** menu.

- 3. Select the appropriate DT9862 Series module from the **Board** list box.

- **4.** In the **Count Duration** text box, enter the number of seconds during which events will be counted.

- **5.** Click **Start** to start the frequency measurement operation.

The operation automatically stops after the number of seconds you specified has elapsed, and the frequency is displayed on the screen.

- **6.** Click **Stop** to stop the frequency measurement operation.

# **Testing Pulse Output**

To verify that the module can perform a pulse output operation, perform the following steps:

1. Connect a scope to counter/timer 0 on the DT9862 Series module. Refer to page 52 for an example of how to connect a scope (a pulse output) to counter/timer 0.

**Note:** The Quick DataAcq application works only with counter/timer 0.

- 2. In the Quick DataAcq application, choose Pulse Generator from the Control menu.

- 3. Select the appropriate DT9862 Series module from the Board list box.

- **4.** Select either **Continuous** to output a continuous pulse stream or **One Shot** to output one pulse.

- 5. Select either **Low-to-high** to output a rising-edge pulse (the high portion of the total pulse output period is the active portion of the signal) or **High-to-low** to output a falling-edge pulse (the low portion of the total pulse output period is the active portion of the signal).

- **6.** Under **Pulse Width**, enter a percentage or use the slider to select a percentage for the pulse width. The percentage determines the duty cycle of the pulse.

- 7. Click **Start** to generate the pulse(s). *The application displays the results both in text and graphical form.*

- **8.** Click **Stop** to stop a continuous pulse output operation. One-shot pulse output operations stop automatically.

# Part 2: Using Your Module

# **Principles of Operation**

| Analog Input Features       | 69 |

|-----------------------------|----|

| Analog Output Features      | 79 |

| Digital I/O Features        | 86 |

| Counter/Timer Features      | 88 |

| Ouadrature Decoder Features | 96 |

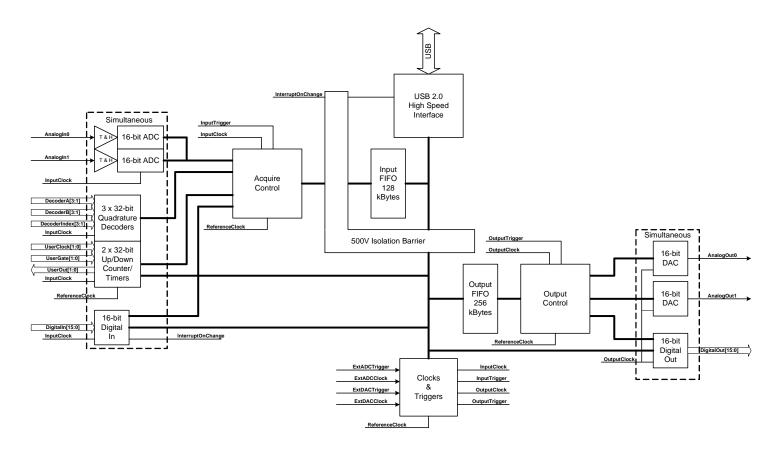

Figure 24 shows a block diagram of the DT9862 Series modules.

Figure 24: Block Diagram of the DT9862 Series Modules

# Analog Input Features

This section describes the following features of analog input (A/D) operations on the DT9862 Series modules:

- Input resolution, described below

- · Analog input channels, described below

- Input ranges, described on page 72

- Input sample clock sources, described on page 72

- Analog input conversion modes, described on page 74

- Input triggers, described on page 76

- Data format and transfer, described on page 77

- Error conditions, described on page 77

#### **Input Resolution**

Input resolution is fixed at 16 bits; you cannot specify the resolution in software.

### **Analog Input Channels**

The DT9862 Series modules support two simultaneous analog inputs. You can connect the analog input channels in single-ended mode to the SMA connectors on the module. In this mode, the source of the input should be close to the module, and all the input signals are referred to the same common ground.

**Note:** To maintain simultaneous operation, all analog input connections must have the same lead lengths.

The DT9862 Series module can acquire data from a single analog input channel or from both analog input channels specified in a channel list. Channels are numbered 0 and 1.

The following subsections describe how to specify the channels.

# Specifying a Single Analog Input Channel

The simplest way to acquire data from a single analog input channel is to specify the channel for a single-value analog input operation using software; refer to page 74 for more information about single-value operations.

You can also specify a single channel using the analog input channel list, described in the next section.

#### Specifying One or More Analog Input Channels

You can read data from one or more analog input channels using an analog input channel list. Because these modules feature simultaneous sampling, the order of the channels in the channel list does not matter. You cannot specify the same channel more than once in the list.

Using software, specify the channels that you want to sample. You can enter up to 13 entries in the channel list for the DT9862 Series module, including the analog input channels, digital input port, two 32-bit counter/timers, and three 32-bit quadrature decoders.

Channels 0 and 1 are reserved for analog input.

#### Specifying the Digital Input Port in the Analog Input Channel List

The DT9862 Series modules allow you to read the digital input port (all 16 digital input lines) using the analog input channel list. This feature is particularly useful when you want to correlate the timing of analog input and digital input events.

To read the digital input port, specify channel 2 in the analog input channel list. You can enter this channel anywhere in the list.

The digital input port is treated like any other channel in the analog input channel list; therefore, all the clocking, triggering, and conversion modes supported for analog input channels are supported for the digital input port, if you specify them this way.

#### Specifying Counter/Timers in the Analog Input Channel List

The DT9862 Series modules allow you to read the value of the 32-bit counter/timer channels using the analog input channel list. This feature is particularly useful when you want to correlate the timing of analog input and counter/timer events.

To read a counter/timer channel, specify the appropriate channel numbers in the analog input channel list (refer to Table 3 on page 71). You can enter the channel number anywhere in the list.

You need two channel list entries to read one 32-bit counter value. The first entry stores the lower 16-bit word, and the second entry stores the upper 16-bit word. You must specify both channel list entries, in sequential order, to include a counter/timer channel.

Table 3 lists the channel number(s) to use for each counter/timer.

Table 3: Using Counter/Timers in Analog Input Channel List

| Counter/Timer<br>Channel | Description                       | Channel to Specify in the<br>Channel List |

|--------------------------|-----------------------------------|-------------------------------------------|

| C/T_0_LOW                | Lower 16 bits (0 to 15) of C/T 0  | Channel 3                                 |

| C/T_0_HI                 | Upper 16 bits (16 to 31) of C/T 0 | Channel 4                                 |

| C/T_1_LOW                | Lower 16 bits (0 to 15) of C/T 1  | Channel 5                                 |

| C/T_1_HI                 | Upper 16 bits (16 to 31) of C/T 1 | Channel 6                                 |

The counter/timer channel is treated like any other channel in the analog input channel list; therefore, all the clocking, triggering, and conversion modes supported for analog input channels are supported for the counter/timers, if you specify them this way.

#### Specifying Quadrature Decoders in the Analog Input Channel List

The DT9862 Series modules allow you to read the value of the 32-bit quadrature decoder channels using the analog input channel list. This feature is particularly useful when you want to correlate the timing of analog input measurements with rotational information.

To read a quadrature decoder channel, specify the appropriate channel numbers in the analog input channel list (refer to Table 4 on page 71). You can enter a channel number anywhere in the list.

You need two channel list entries to read one 32-bit counter value. The first entry stores the lower 16-bit word, and the second entry stores the upper 16-bit word. You must specify both channel list entries to include a quadrature decoder channel.

Table 4 lists the channel number(s) to use for each quadrature decoder.

**Table 4: Using Quadrature Decoders in Analog Input Channel List**

| Quadrature<br>Decoder Channel | Description            | Channel to Specify in the Channel List |

|-------------------------------|------------------------|----------------------------------------|

| QUAD_0_LOW                    | Lower 16 bits of Q/D 0 | Channel 7                              |